MAX+PLUS II(可编程逻辑设计软件)——经典PLD开发环境,工程师的入门首选与怀旧利器

MAX+PLUS II 是 Altera 公司推出的上一代专业级可编程逻辑器件(PLD)集成开发环境,专为 FPGA 与 CPLD 设计打造。它以极简操作逻辑、全链路设计支持(原理图/文本双输入、时序与功能仿真、高速编译、器件编程下载)和零学习门槛著称,曾是全球高校电子类课程及初学者入门 PLD 开发的标配工具。虽已由 Quartus II 接替官方维护,但其轻量、稳定、兼容性强的特点,仍使其在教学实践、老项目维护与嵌入式逻辑快速验证场景中不可替代。本版为绿色破解版,免激活直用,开箱即投入数字电路设计实战。

为什么选择 MAX+PLUS II?

作为业界公认的“最易上手 EDA 工具”,MAX+PLUS II 不仅延续了 Altera 在可编程逻辑领域的技术积淀,更以高度人性化的交互逻辑降低硬件设计门槛。它不依赖复杂配置,无需高性能工作站,Windows XP/7 系统即可流畅运行;从输入第一个逻辑门到生成下载文件,全程可视化指引清晰,特别适合电子工程专业学生、硬件爱好者及中小规模逻辑开发人员快速构建原型、完成课程设计或复刻经典数字系统。

核心特性一览

开放的协同接口

无缝对接 Cadence、Mentor Graphics、Synplicity、Viewlogic 等主流 EDA 平台,支持设计数据双向导入导出,便于融入多工具协作流程。

真正与器件结构无关的设计环境

内置统一 Compiler 核心,全面支持 Altera 全系列经典器件:FLEX10K/8000/6000、MAX9000/7000/5000 及 Classic 系列。设计逻辑无需绑定具体芯片架构,一次编写,多平台适配。

全流程一体化集成开发

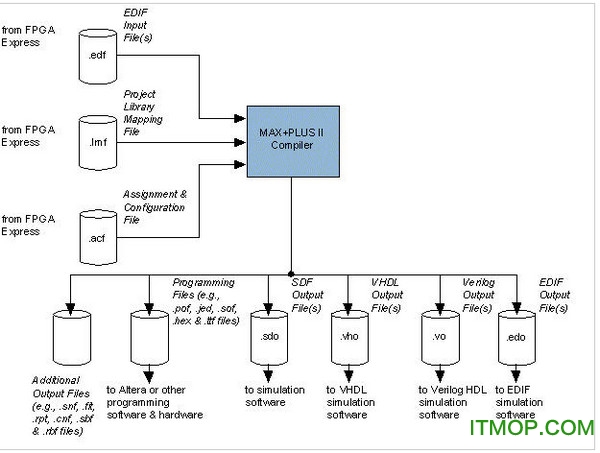

设计输入(原理图/Schematic、文本/Text)、逻辑综合、器件适配(Fitting)、时序分析、功能与时序仿真、编程下载全部集成于单一界面,显著缩短迭代周期,提升调试效率。

海量可复用设计资源库

内置完整 74 系列标准逻辑器件模型,同时提供宏功能(Macro-Function)与参数化兆功能(Megafuction)模块,覆盖计数器、状态机、存储器控制器等常用数字模块,大幅减少底层重复开发。

灵活可定制的模块化架构

允许用户按需启用或禁用各类设计输入方式(如 AHDL、VHDL、Verilog HDL)、仿真引擎与编程选项,打造专属高效工作流。

多语言硬件描述支持

原生兼容 VHDL、Verilog HDL 及 Altera 自研高级硬件描述语言 AHDL,兼顾国际标准与本土化教学需求,助力不同基础用户平滑进阶。

开放核(OpenCore)扩展能力

支持自定义宏函数添加与封装,设计者可将高频使用逻辑单元保存为可调用 IP 模块,实现知识沉淀与团队复用。

PLD 是什么?一文读懂可编程逻辑的本质

PLD(Programmable Logic Device,可编程逻辑器件)是一类可通过软件配置改变内部逻辑功能的数字集成电路。它兼具通用芯片的灵活性与专用芯片(ASIC)的功能性——未编程时是标准通用器件,烧录后即成为满足特定应用需求的定制化逻辑系统。

相较于传统 ASIC 设计需经历前端设计、版图绘制、流片生产、测试验证等漫长高成本流程,PLD 允许工程师跳过物理制造环节,直接通过编程定义逻辑行为与互连关系,实现“所想即所得”。从早期 PROM、PAL、GAL 到后期 CPLD、FPGA,PLD 的演进始终围绕两大核心:如何动态重构逻辑门功能?如何灵活重配信号通路?MAX+PLUS II 正是驾驭这一能力的经典载体。

绿色破解版安装指南(精简实操版)

1. 运行安装目录下 PCALTERA32BIT\SETUP.EXE,选择 Install Software → MAX+PLUS II BASELINE Software,连续点击 Next 完成基础安装;

2. 首次启动时出现许可协议窗口,请滚动至底部并点击 OK;

3. 将压缩包内提供的授权文件(通常为 license.dat 或类似命名)复制到 MAX+PLUS II 安装根目录(默认路径如 C:\MAXPLUS2);

4. 启动软件,依次点击菜单栏 Option → License Setup,在弹窗中点击 Browse 选中刚复制的授权文件,确认后退出并重启软件;

5. 如需连接下载线(如 ByteBlaster),请进入 Windows 控制面板 → 添加/删除硬件,按向导完成驱动识别与安装(部分系统需手动指定 INF 驱动文件)。